サポート

著作権 © 2009-2024Teledyne LeCroy Xena ApS, Denmark

このセクションは、40G 以上のレートをサポートする高速モジュールのポートにのみ適用されます。これらのモジュールのポートの場合、下図に示すように、メインのResource PropertiesタブにPCS/PMA Config & Statusサブタブが追加表示されます。

PAM4 ポートの場合、RS-FEC は常に有効です。また、ポートでサポートされている場合は、Link Training を有効に し、Autoneg (オートネゴシエーション)を有効にすることもできます。Autoneg を有効にすると、Link Training も有効になり、Autonegotiation の後に実行されます。Clear Countersは、このページのカウンタをクリアします。Allow clearing counters from Global viewをチェックすることで、Global Statistics ページのクリア・カウンタ機能を使用して、このページのカウンタをクリアできます。

このページの残りの部分に表示される内容は、選択したポートの設定によって異なります。

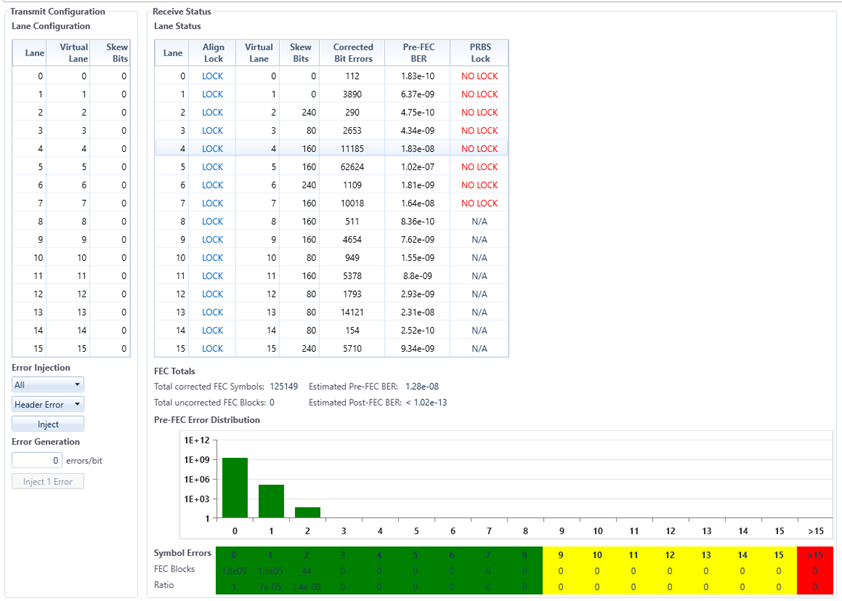

下の画像は、PAM4ポート(この場合は400Gポート)で見えるものを示している:

Transmit Configurationセクションでは、ポートの物理レーンごとに、物理レーンに使用するVirtual Laneを変更し、各レーンのSkew Bitsを設定することができます。

Receive Status セクションでは、各物理レーンについて、アライメントロック中かどうか(Alignment Lock)、物理レーンに使用されている仮想レーン(Virtual Lane)、各レーンのスキュービット(Skew Bits)を確認できる。さらに、各レーンの訂正ビットエラー数と推定 Pre-FEC BERを見ることができます。PRBS Lock列には、ポートから PRBS 信号が生成されているかどうかが表示されます。

ページの下部には、ポートの FEC 統計情報が表示されます:

Pre-FEC Error Distributionグラフもある。ここでは、0、1、2......最大 15 シンボルのエラーを持つ受信 FEC ブロックの数を見ることができる。これはPAM4信号に使用されるRS-FECが修正するものである。また、15シンボルエラー以上の受信FECブロック数を見ることもできます。これは、PAM4信号に使用されるRS-FECが修正できる範囲を超えているため、未修正のFECブロックがカウントされることになり、ほとんどの場合、受信信号の上位レイヤーでもエラーが発生します。

エラー・インジェクションは現在実装されていない。

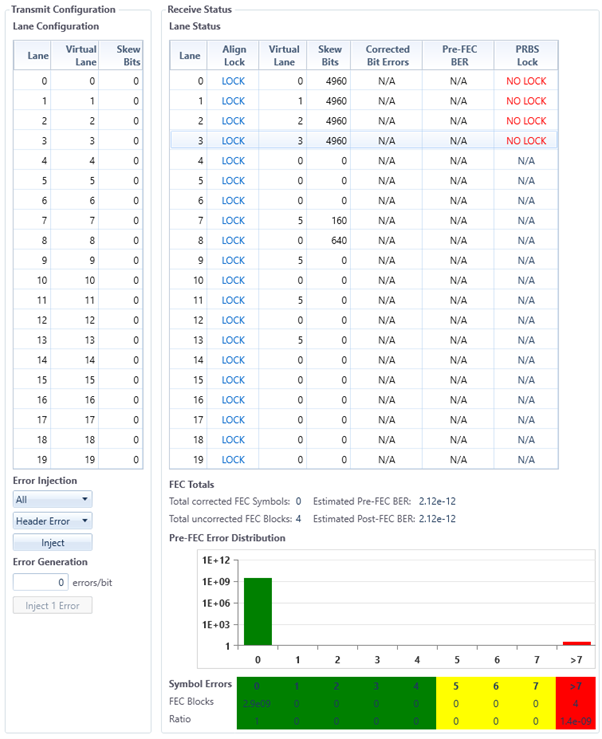

下の画像は、FEC付きのNRZポート(この場合は100Gポート)で見えるものを示している。

ほとんどは、PAM4 ポートで制御および確認できるものと同様です。しかし、送信設定テーブルと受信ステータステーブルの最初の4行だけが実際に使用されることに注意してくださ い。また、NRZ 信号に使用される RS-FEC は最大 7 シンボルのエラーを訂正する。それに応じてPre-FEC Error Distributionグラフも調整される。

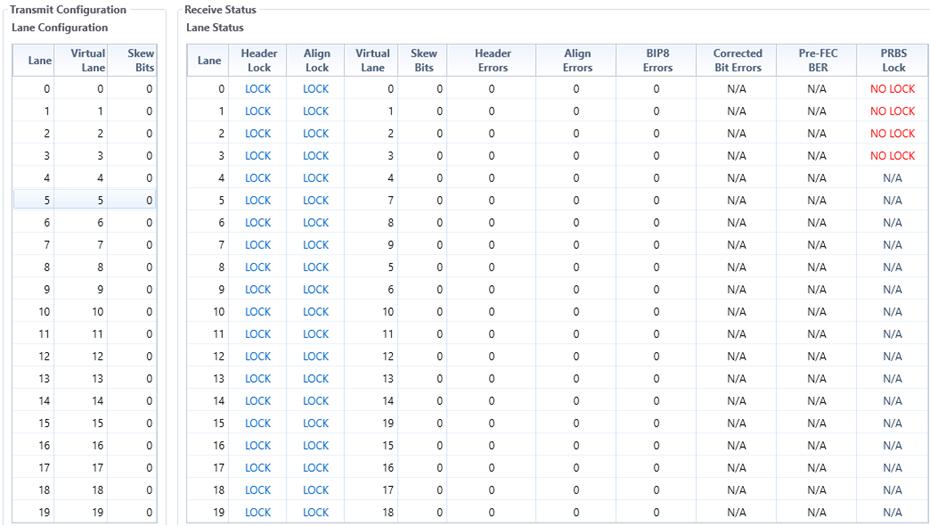

下の画像は、FECなしのNRZポート(この場合は100Gポート)で見えるものを示している。

ほとんどの場合、PAM4 ポートの送信コンフィギュレーションと 受信ステータスのテーブルで制御および確認できるものと同様です。ただし、Receive Status テーブルには、Header Errors、Alignment Errors、およびBIP8 Errors のカウンタが追加されている。RS-FEC を使用しないポートでは、Corrected Bit ErrorsおよびPre-FEC BERカウンタは更新されません。