Award Winning Solutions

Xena has won multiple global awards for price/performance and technical innovation. Learn more.

Technical Expertise

Copyright © 2009-2024 Teledyne LeCroy Xena ApS, Denmark

The E100q Chimera is a 2-port 100GE dual-media test module that can also test 50GE, 40GE, 25GE and 10GE

2-port 100GE test module

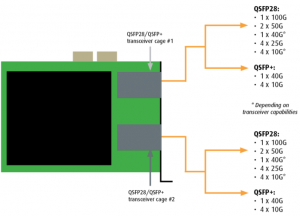

The E100q Chimera is a 2 port 100GE test module that can also test these Ethernet network speeds: 50GE, 40GE, 25GE and 10GE. This unique flexibility is provided via two physical transceiver cages, both supporting QSFP28 and QSFP+ transceivers. Both cages can be active simultaneously.

The result is a highly versatile solution for performance and functional testing of network infrastructure and Ethernet equipment capable of supporting 100GE such as switches, routers, NICs, taps, packet-brokers, and backhaul platforms.

QSFP28: 100G, 50G, 40G*, 25G, and 10G* Ethernet

QSFP+: 40G and 10G Ethernet

*Depending on transceiver capabilities

2x100GE, 4x50GE,2x40GE, 8x25GE, and 8x10GE

1 x 100GBASE-SR4/LR4/CR4 (as per 802.3bj), or

2 x 50GBASE-SR2/LR2/CR2 (as per Consortium), or

1 x 40GBASE-SR4/LR4/CR4 (as per 802.3ba), or

4 x 25GBASE-SR/LR/CR (as per 802.3by/Consortium), or

4 x 10GBASE-SR/LR/CR (as per 02.3ae)

Actual interface options depend on the capabilities of the inserted transceiver.

Both cages must run with the same base interface configuration (e.g. 2 x 100GE)

** As defined by 25/50 GigabitEthernet Consortium

RS-FEC (Reed Solomon) 528,514,t=7, IEEE 802.3 Clause 91 (100GE)

RS-FEC (Reed Solomon) 528,514,t=7, IEEE 802.3 Clause 108 (25GE)

RS-FEC (Reed Solomon) 528,514,t=7, 25G Ethernet Consortium (25GE)

2 x QSFP28/QSFP+

Link state, FCS errors, frame and byte counters

Lock Tx clock to recovered Rx clock from any input port (Single clock domain)

System is fully field upgradeable to product releases (FPGA images and Software)

Enable/disable of optical laser

Sub 1 μs delay (depending on port speed)

Single short or repeatable link down events with ms precision

Repeatable error inject periods at PMA layer with ms precision

Ethernet packets from 56 to 12288 bytes

8 (incl. default flow)

Any protocol within the first 128 packet bytes. This includes:

• Ethernet (DMAC / SMAC)

• Any number of VLAN tags.

• Any number of MPLS labels.

• IPv4 / IPV6

• UDP / TCP

• eCPRI / RoE

• Custom data fields.

• Xena Payload ID (Xena proprietary)

Chimera implements impairment counters per flow, including dropped, corrupted, mis-ordered and

duplicated packets.

Impairments can be changed dynamically

Packet drop

Duplication

Mis-ordering

Protocol Corruption (Ethernet Frame FCS, IP/UDP/TCP header Check Sum error)

Constant latency

• Max. latency lossless 160ms (100GE wire-speed) Step-size 100 ns, accuracy: +/- 50 ns

• Max. latency reduced bandwidth 1.6 s (19.5 sec)

• Min. (Intrinsic) delay: 7.0 μs for 40G/50G/100G

7.2 μs for 25G

13.0 μs for 10G

Accumulate & Burst

Step (2 alternating delays)

Jitter (Distributions – see below)

Drop, duplication and corruption probability is configurable up to 100%. Step size: 0.0001%

Impairments and jitter (Duplication, Drop, Corruption and latency) can be applied with very flexible

distributions including Random, Periodic, Gilbert-Elliot, Gaussian, Gamma and Uniform. You can also

specify custom distributions to be used with impairments.

Policing – Step size: 100 kbps

Shaping – Step size: 100 kbps